Processor Status Register

The Processor Status Register (abbreviated as P) is a hardware register which records the condition of the CPU as a result of arithmetic, logical or command operations. The purpose of the Processor Status Register is to hold information about the most recently performed ALU operation, control the enabling and disabling of interrupts and set the CPU operating mode.

Flags[edit | edit source]

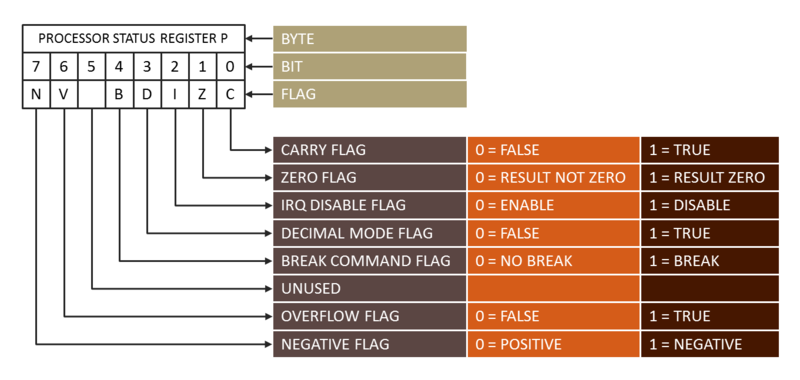

The condition of the MOS Technology 65xx CPUs is recorded by seven combined processor flags and control flags (all within a single byte). Each flag corresponds to a single bit within the Processor Status Register (refered as register P) which are explicitly or implicitly read and/or written. The meaning of a bit is either set (1 or true) or cleared (0 or false). Table 1 lists the seven flags (as named by MOS Technology) in the Processor Status Register.

| Table 1 - Flags of the MOS Technology 65xx Processor Status Register | |||

|---|---|---|---|

| Bit | Flag | Abbreviation | Purpose |

| 0 | Carry Flag | C | Indicates when a bit of the result is to be carried to or borrowed from another byte. Also used for rotate and shift operations. |

| 1 | Zero Flag | Z | A one indicates that the result of an operation is equal to zero. |

| 2 | Interrupt Disable Flag | I | If set IRQ will be prevented (masked), except non-maskable interrupts (NMI). |

| 3 | Decimal Mode Flag | D | If set arithmetic operations are calculated in decimal mode (otherwise usually in binary mode). |

| 4 | Break Command Flag | B | Indicates that interrupt request has been triggered by an BRK opcode (not an IRQ). |

| 5 | Unused | - | Cannot be changed, usually 1. |

| 6 | Overflow Flag | V | Indicates that a result of an signed arithmetic operation exceeds the signed value range (-128 to 127). |

| 7 | Negative Flag | N | A value of 1 indicates that the result is negative (bit 7 is set, for a two's complement representation). |

Diagrammatically this can be seen as:

The most commonly used flags are C (bit 0), Z (bit 1), N (bit 7).

Links[edit | edit source]

- Sander, Louis F, The Status Register, Compute!, October 1984, Page 134, accessed 30 October 2014.

- Chasin, Mark, Assembly Language Programming for the Atari Computers, accessed 30 October 2014.